# 高性能嵌入式人工智能 SOC 芯片 Yulong810A 数据手册

(Ver: 1.16)

#### 珠海欧比特宇航科技股份有限公司

地址: 广东省珠海市唐家东岸白沙路 1 号欧比特科技园邮编: 519080 电话: 0756-3391979 传真: 0756-3391980 网址: www.myorbita.net

# 版权声明

珠海欧比特宇航科技股份有限公司拥有此文件的版权,并有权将其作为保密资料处理。 本文件包含由版权法保护的专有资料,未经珠海欧比特宇航科技股份有限公司的书面同意不 得将本文件的任何部分进行照相、复制、公开、转载或以其他方式散发给第三方,否则,必 将追究其法律责任。

# 免责声明

本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新, 恕不另行通知。 如因文档使用不当造成的直接或间接损失, 珠海欧比特宇航科技股份有限公司不承担任何责任。

# 珠海欧比特宇航科技股份有限公司

ZHUHAI ORBITA AEROSPACE SCIENCE& TECHNOLOGY CO.,LTD

地址(Addr): 广东省珠海市唐家东岸白沙路 1 号欧比特科技园

OrbitaTechPark, 1 Baisha Road, Tangjia Dong'an, Zhuhai, Guangdong, China

邮编: 519080

电话(Tel): +86 756-3391979

传真(Fax): +86 756-3391980

网址(web): www.myorbita.net

# 目录

| . 慨还                                                                                                  |                |

|-------------------------------------------------------------------------------------------------------|----------------|

| 1.1 简介<br>1.2 结构组成<br>1.3 主要特征<br>1.4 模块说明                                                            | 5<br>7         |

| 2. 封装和信号定义                                                                                            | 20             |

| 2.1 封装信息         2.2 封装信号引脚定义         2.3 封装电源引脚定义                                                    | 22             |

| 3. 工作条件及电气特性                                                                                          |                |

| 3.1 PVT SENSOR 电气特性                                                                                   | 44<br>44<br>45 |

| . 系统                                                                                                  | 47             |

| 4.1 复位<br>4.2 时钟<br>4.3 电源管理与低功耗模式<br>4.3.1 电源架构<br>4.3.2 供电<br>4.3.3 最大功率<br>4.3.4 电源模式<br>4.3.5 电源域 |                |

| 4.3.6 通断电顺序<br>4.3.7 电源管理单元(PMU)                                                                      |                |

| 5. RTC 供电及上下电方式                                                                                       |                |

| · RTC 人名文工   名力 Д                                                                                     |                |

| · 冲场                                                                                                  |                |

| • / 川り火口心                                                                                             |                |

| 表   | 目 | 录 |

|-----|---|---|

| ~ ~ | , |   |

| 表 1-1 芯片模块说明表                                             | 12 |

|-----------------------------------------------------------|----|

| 表 2-1 FCBGA896 封装尺寸说明                                     | 21 |

| 表 2-2 芯片引脚信号表                                             | 22 |

| 表 2-3 封装电源引脚定义表                                           | 37 |

| 表 3-1 PVT SENSOR 电气特性                                     | 44 |

| 表 3-2 SAR ADC 电气特性表                                       | 44 |

| 表 3-3 RTC 模块电特性表                                          | 45 |

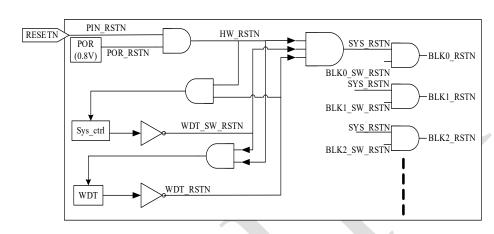

| 表 4-1 复位信号分类表                                             | 47 |

| 表 4-2 各 PLL 支持的最大频率                                       | 51 |

| 表 4-3 各子时钟最大频率                                            | 52 |

| 表 4-4 YuLong810A 供电说明                                     | 57 |

| 表 4-5 电源轨最大功率                                             | 58 |

| 表 4-6 YULONG810A 低功耗模式定义                                  | 59 |

| 表 4-7 YULONG810A 电源域定义                                    | 60 |

| 表 6-1 内部 BOOT 和外部 EMI 启动方式选择列表                            | 65 |

| 表 6-2 内部 BOOT 启动方式选择表                                     | 65 |

| 表 7-1 芯片产品订货信息                                            | 67 |

|                                                           |    |

| <b>阿</b> 日亭                                               |    |

| 图1.17/www.co.co.co.co.co.co.co.co.co.co.co.co.co.         | 5  |

| 图 2.1YULONG810A 芯片框图                                      |    |

| 图 2-1YULONG810A 芯片 FCBGA896 封装外形图<br>图 2-2 FCBGA896 封装外形图 |    |

|                                                           |    |

| 图 4-1 芯片复位信号控制图                                           |    |

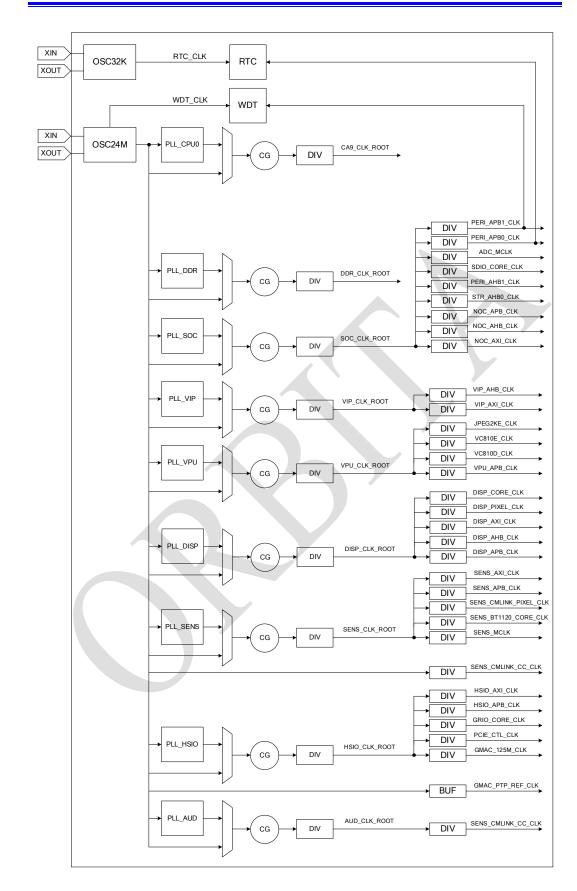

| 图 4-2 芯片时钟结构图                                             |    |

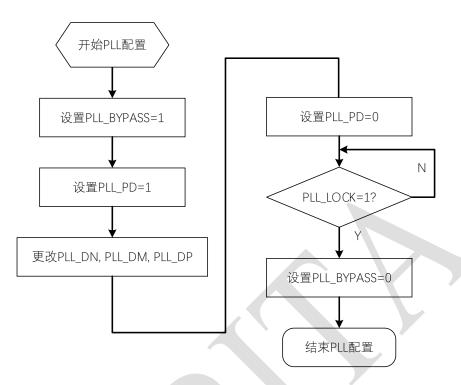

| 图 4-3 PLL 配置流程图                                           |    |

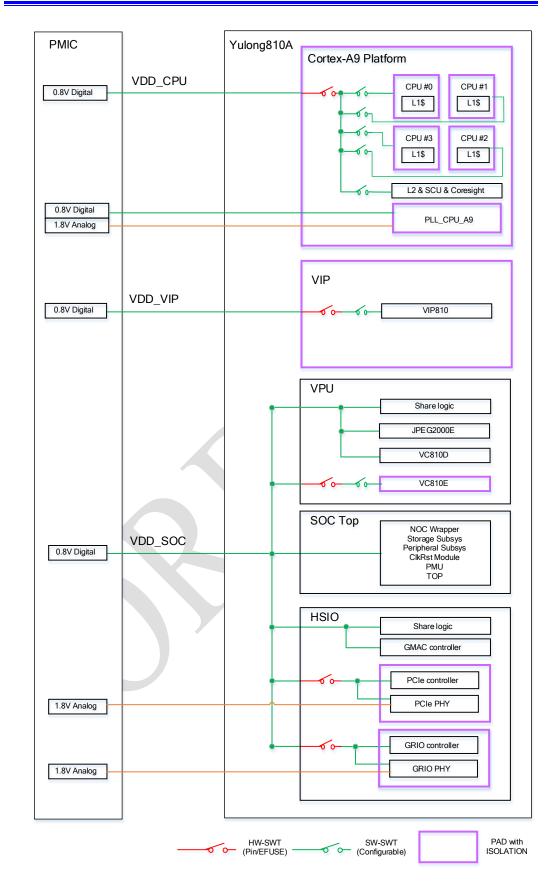

| 图 4-4(A) YULONG810A 电源结构                                  |    |

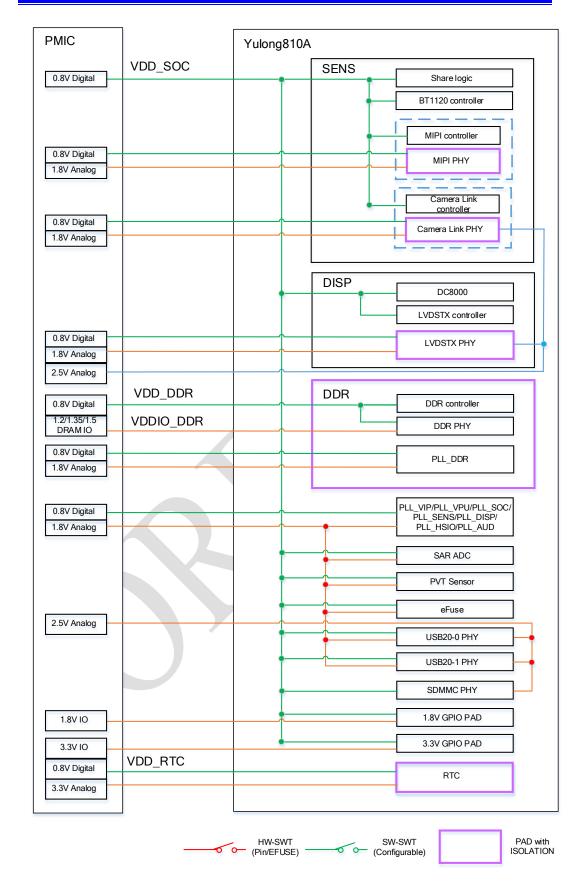

| 图 4-4(B) YULONG810A 电源结构                                  |    |

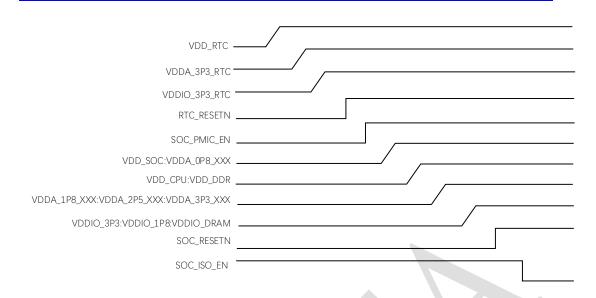

| 图 4-5 YULONG810A 上电顺序                                     |    |

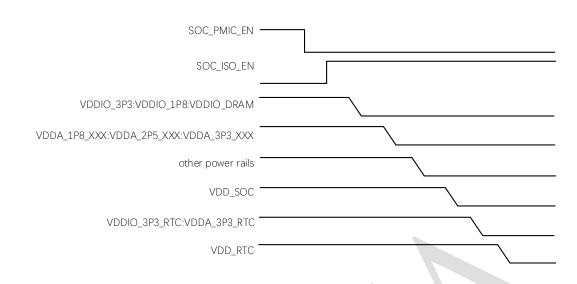

| 图 4-6 YULONG810A 断电顺序                                     |    |

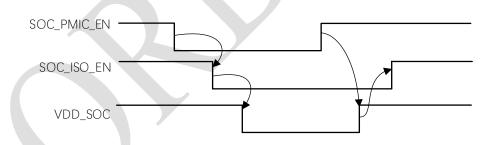

| 以 4- / VIII ONGX I DA 与 PM I ( ) / III 的时 区               | 63 |

# 1. 概述

## 1.1 简介

Yulong810A是欧比特公司推出的新一代嵌入式人工智能系列处理器芯片,芯片聚焦于前端图像处理、前端信号处理和智能控制,芯片具有深度学习、神经网络算法的平台加速能力。Yulong810A芯片为异构多核架构(CPU+AI加速器),采用FD-SOI生产工艺,具有高性能、高可靠、低功耗的特点,芯片面向航空航天、智能安防、机器人、AIoT、智能制造、智慧交通等应用场景。

Yulong810A芯片集成4核ARM Cortex-A9处理器。处理器内部包含整型处理单元(IU)、浮点处理单元(FPU)、高速一级缓存(L1 Cache)、存储器管理单元(MMU)、NEON协处理器和高速二级缓存(L2 Cache)等模块。可为客户应用程序提供充足、可靠的计算资源。

Yulong810A芯片集成H.265/264/JPEG编解码器以及JPEG2000编码器,提供高性能视频图像编解码功能支持。

Yulong810A芯片內部集成了丰富的片上外设,包括CameraLink,MIPI,BT1120, LVDS Display, RapidIO, PCIe, GigaEthernet, USB2.0, Nand Flash控制器, SPI Nor Flash控制器, SDIO, 1M/10M的1553B总线控制器, CAN总线控制器, EMI控制器, SPI主控器, I<sup>2</sup>C主控器, I<sup>2</sup>S控制器, UART, 定时器, RTC, DMA, Watchdog, GPIO, PWM, SM4加解密引擎等功能模块,能够满足各类应用需求。

Yulong810A芯片集成了完备的片上调试系统。对于ARM A9内核,用户可以通过JTAG接口连接CoreSight调试模块来访问芯片内部的寄存器、存储器和片内外设,进行软硬件调试。

Yulong810A配套欧比特提供的SDK,方便客户快速高效地进行AI软件程序的 开发。 支持 Google TensorFlow、 Caffe 等 AI 开发框架, 支持 OPENCL\OPENVX\OPENCV等软件库,可以进行AI开发。支持eCOS、VxWorks、Linux等实时嵌入式操作系统,用户可方便地实现嵌入式实时控制系统的高性能

多核并行处理设计。

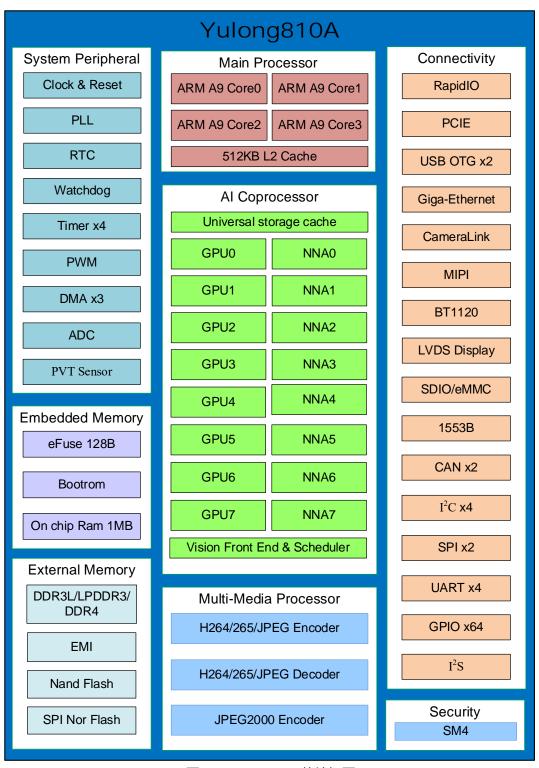

# 1.2 结构组成

图 1-1Yulong810A 芯片框图

#### 图1-1中各个模块的说明如下:

- 1) ARM A9: ARM A9 处理器核心, 共 4 个;

- 2) 512KB L2Cache (ARM): ARM A9 处理器 L2Cache 模块;

- 3) AI Coprocessor: AI 协处理器 VIP810;

- 4) Universal Storage Cache: AI 协处理器 Cache;

- 5) GPU: 图形处理器, 共8个;

- 6) NNA: 神经网络加速单元, 共8个;

- 7) Vision Front End& Scheduler: AI 协处理器任务分配、命令处理单元;

- 8) DDR: DDR 控制器, 支持 DDR4/DDR3L/LPDDR3;

- 9) On Chip RAM 1MB: 1MB 片上通用 SRAM;

- 10) Clock&Reset: 时钟复位模块;

- 11) PLL: 锁相环模块,用于产生片内各模块的时钟信号;

- 12) RTC: 实时时钟模块;

- 13) Watchdog: 看门狗模块;

- 14) Timer: 定时器模块, 共 4 通道;

- 15) PWM: PWM 生成器;

- 16) DMA: 直接内存存取模块, 共3组, 每组包含8通道;

- 17) ADC: 12 位精度 SAR ADC;

- 18) PVT sensor: 电压/温度传感器;

- 19) H.264/H.265/JPEG Encoder: H254、H.265 编码器模块 VC810E;

- 20) H.264/H.265/JPEG Decoder: H.264、H.265 解码器模块 VC810D;

- 21) JPEG2000 Encoder: JPEG2000 编码器模块;

- 22) EFuse 128B: 128Byte Efuse 控制器;

- 23) BOOTROM: ARM BOOTROM 模块;

- 24) EMI: 外部存储器接口(External Memory Interface);

- 25) Nand Flash: Nand Flash 控制器;

- 26) SPI Nor Flash: SPI Nor Flash 控制器;

- 27) RapidIO: RapidIO 控制器, 片内集成 PHY;

- 28) PCIE: PCIE 控制器,支持 PCIE Gen1、GEN2 协议;

- 29) USB OTG: USB2.0 主控制器, 共 2 路;

- 30) Giga-Ethernet: 千兆以太网控制器,支持片外外接 PHY;

- 31) Camera Link: Camera Link 图像接口, 支持 Camera Link 2.0 标准;

- 32) MIPI: MIPI CSI-2 控制器:

- 33) BT1120: BT1120 接口;

- 34) LVDS Display: LVDS 视频输出控制器,片内集成 LVDS TX PHY;

- 35) SDIO/eMMC: SDIO/eMMC 控制器, 支持 SD3.0 及 eMMC v4.5;

- 36) CAN: CAN 总线控制器, 共 2 通道;

- 37) 1553B: 1553B 总线控制器;

- 38) GPIO: 独立可配置 GPIO 信号, 共 64 路;

- 39) I<sup>2</sup>C: I<sup>2</sup>C 总线控制器, 共 4 通道;

- 40) I<sup>2</sup>S: I<sup>2</sup>S 总线控制器;

- 41) SPI: SPI 接口, 支持主/从模式, 共 2 通道;

- 42) UART: 4路通用串行接口;

- 43) SM4: SM4 加解密模块。

### 1.3 主要特征

#### > 主处理器

- 4核 ARM CortexA9 处理器

- -工作频率范围 1GHz@0.8V(Typical Case);

- 32KB L1 Instruction Cache:

- 32KB L1 Data Cache;

- -核内定时器及看门狗模块:

- 512KB L2 Cache;

- -包含 NEON 浮点向量协处理单元;

# > AI 协处理器

- GPU 单元

- -标准 shader core;

- -支持 EVIS 扩展指令:

- -支持 16/32/64 位浮点运算;

- -峰值算力 64 GFLOPS;

- NNA 单元

- -矩阵式并行卷积 MAC 单元;

- -支持神经网络多维数组处理的压缩和剪枝;

- -支持 8/16 位定点处理;

- -峰值算力 12 TOPS;

#### > 图像协处理单元

- H.264/H.265/JPEG 编码器

- -HEVC 编码性能 3840x2160@30fps (main10 level5.1);

- -H.264 编码性能 3840x2160@30fps (high profile);

- JPEG 编码性能 3840x2160@30fps;

- -输出格式 YCbCr 4:2:0;

- -支持采样位深度 8bpc;

- -支持图像降采样;

- -支持切片/帧类型: I, P, B 三种;

- H.264/H.265/JPEG 解码器

- -HEVC 解码性能 3840x2160@30fps (main10 level5.1);

- -H.264 解码性能 3840x2160@30fps (high level5.2);

- JPEG 解码性能 3840x2160@30fps;

- -支持后处理 (post processing) 输出;

- -支持 OpenMax IL API;

- -支持 Libva 及 Libdrm;

- -支持嵌入式参考帧压缩;

- JPEG2000 编码器

- -支持的采样格式:

- -灰度级采样;

- -双元素: 4:4, 4:2, 4:1 及 4:0;

- -三元素: 4:4:4, 4:2:2, 4:1:1 及 4:2:0;

- -四元素: 4:4:4:4, 4:2:2:2, 4:1:1:1 及 4:2:0:0;

- -支持 8bit 每元素的采样精度;

- -支持高达 65535 x 65535 图像分辨率;

- -支持 4096 x 2160 分片精度;

- -支持有损或无损压缩;

- -支持单/多品质层编码;

- -支持标准兼容码流(JPC)或文件(JP2)输出;

#### ▶ 存储系统

- Bootrom: 内嵌 BOOT 程序;

- OCM: 1MB 片内 RAM:

- 外部存储器接口

- -DDR4/DDR3L/LPDDR3: 最高数据率 2666Mbps, 3GB 存储空间, 64bit 数据宽度, 8bit ECC;

- -NAND Flash: 支持 8bit/16bit 数据宽度, 支持 512KB/2KB/4KB/8KB 页尺寸, 24bit ECC;

- -串行 Nor Flash: 标准/双/四 SPI 接口,最高数据率 50Mbps,支持主/从模式:

- -并行 Nor Flash 或异步 SRAM: 支持 8bit/16bit 数据宽度, 32MB 存储空间, 支持 16 位启动;

#### ▶ 高速外设接口

- 显示

- -LVDS 串行接口,最高支持 FHD 分辨率;

- 摄像头传感器

- -Camera Link 摄像头接口, v2.0 标准, 支持 Lite/Base/Medium/Full模式;

- -MIPI CSI-2 串行摄像头接口,支持 4 通道;

- BT1120 摄像头接口;

- 高速串行接口

- -PCIe Gen2 接口,支持 4 通道,支持 Root 复杂操作以及 Endpoint操作:

- -Rapid IO Gen2 接口,支持 4 通道,支持 BRC1 5Gbps 及 BRC2 6.25Gbps;

- -10/100/1000 Mpbs 以太网;

- USB2.0 接口, 2 路

- USB2.0-OTG;

- USB2.0 Host only;

- SD/SDIO/MMC 接口

- -支持 SD3.0 及 eMMCv4.5 标准;

- -支持 4 比特 SD 及 SDIO 传输模式标准,支持最高 UHS-I SDR-104 模式 (最大 104 MB/s);

- -支持 4 比特或 8 比特 MMC 卡传输模式标准, 支持 SDR 及 DDR 模式最高 52MHz (最大 104 MB/s);

#### > 系统组件

- RTC: 报警和计时功能;

- Watchdog: 16 位看门狗计数器;

- Timer: 4 通道 32 位普通定时器;

- DMA: 3组,每组8通道控制器;

#### ▶ 低速外设接口

- I<sup>2</sup>S: 支持 24bit 立体声输入/输出;

- UART: 4路,支持2线标准,支持流控制;

- I<sup>2</sup>C: 4 路,支持主/从模式,最高 3.4Mbps;

- SPI: 2路, 支持主/从模式;

- GPIO: 64 路独立可配置 GPIO 信号,支持 GPIO 中断功能;

- SAR ADC: 12bit 精度, 采样率最高支持 1MSPS;

- 1553B:

- -支持BC、RT和BM三种工作模式;

- -数据传输速率 1Mbps 和 10Mbps 可配置;

- CAN:

- -两个独立通道;

- -支持 PeliCAN 和 BasicCAN 两种模式;

- -符合 CAN 2.0B 协议;

- JTAG 调试接口;

#### ▶ 电源管理及控制

- 集成片内电源管理单元;

- 集成温度传感器:

- 支持多种系统功耗模式;

- 集成灵活的门控时钟设计;

#### > 安全功能

- 片上 128Byte eFUSE;

- SM4 数据安全模块;

#### ▶ 其他

- 芯片封装: FCBGA 896, 25\*25mm, 0.8pitch;

- 工艺: 22 nm FDX 工艺;

- 工作电压: Core 0.8V, 数字 IO 1.8V/3.3V, Analog 1.8V/2.5V/3.3V, DDR IO 1.2V/1.35V/1.5V;

- 工作温度: -40℃~ +125℃;

- 典型功耗: 5W;

- 抗辐指标: SEL 免疫;

## > 软件支持

- 异构多核(API)接口:OPENCL、OPENVX;

- 操作系统 (EOS): Linux、FreeRTOS;

- 设备驱动程序及例程。

# 1.4 模块说明

Yulong810A 芯片包含以下模块:

表 1-1 芯片模块说明表

|                                      | 表 1-1 芯片模块说明表 |                                                                                                                                                                                                                                                                 |  |

|--------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 模块名称                                 | 模块数量          | 模块功能                                                                                                                                                                                                                                                            |  |

| Main Processor                       | 1             | 4核SMP架构ARM Cortex A9处理器。每个核包含超标量可变长度8级流水线,支持乱序执行,具有动态分支预测功能。完全实现ARM体系结构v7-A指令集、ARM Neon Advanced SIMD(单指令,多数据)支持加速媒体和信号处理计算。集成PL310 L2 Cache。集成CoreSight调试单元,支持基于JTAG硬件断点、多核调试。                                                                                 |  |

| AI Coprocessor<br>(VIP810)           | l             | 芯片 AI 协处理器主要由 GPU 可编程引擎和神经网络引擎(Neural Network Engine,NN)两大部分组成,包含 8 路 GPU 和 8 路 NN 加速单元。可编程引擎 GPU 由标准 shader core 构成,并在 Shader 指令集的基础上增加了 24 条增强指令集 EVIS(Enhanced Vision Instruction Set),NN 单元由乘累加器(MAC)阵列组成,可进行 8 位、16 位定点运算。AI 协处理器通过 OPENCL\OPENVX 等软件接口编程。 |  |

| H264/265/JPEG<br>Encoder<br>(VC810E) | 1             | H264/265/JPEG 编码器支持 H.264,H.265 及 JPEG 格式编码。 该编码器包括编码内核模块、控制寄存器、中断控制器、计时器。系统 CPU 使用 APB 接口控制编码内核模块(配置编码器参数,开始处理,获取状态和结果),编码器通过 AXI4 接口从 Memory 中读写视频数据。                                                                                                         |  |

| H264/265/JPEG<br>Decoder<br>(VC810D) | 1             | H264/265/JPEG 解码器支持 H.264, H.265, SVC, MVC 及 JPEG 格式解码。 解码器包括解码器内核、控制寄存器、中断控制器、计时器。系统 CPU 使用 APB 接口控制解码器模块(配置解码器参数,开始处理,获取状态和结果),解码器通过 AXI4 接口从 Memory 中读写视频数据。该解码器执行像素级/低级处理,控制软件处理高                                                                           |  |

| 模块名称             | 模块数量 | 模块功能                                 |  |

|------------------|------|--------------------------------------|--|

|                  |      | 于切片数据级别的更高级别的解码过程。                   |  |

|                  |      | JPEG2000编码器支持JPEG2000 PART 1有损及      |  |

|                  |      | 无损图像压缩。                              |  |

|                  |      | JPEG2000模块能够高速、高质量地对JPEG 2000        |  |

|                  |      | 图像和视频进行编码。该模块执行以下视频编码压缩              |  |

|                  |      | 操作:                                  |  |

| IDEC 2000 E 1    |      | ◆无损或有损压缩;                            |  |

| JPEG2000 Encoder | 1    | ◆先进比特率控制引擎;                          |  |

|                  |      | ◆单或多质量层编码;                           |  |

|                  |      | ◆CPRL进展顺序;                           |  |

|                  |      | ◆LRCP进展顺序(仅灰度级);                     |  |

|                  |      | ◆错误复原编码特性;                           |  |

|                  |      | ◆标准兼容码流(JPC)文件(JP2)输出;               |  |

|                  |      | DDR 控制器兼容 JEDEC 标准 DDR4/DDR3L/       |  |

|                  |      | LPDDR3 SDRAM。其中, DDR4 支持最高 2666Mbps, |  |

|                  |      | DDR3L 支持最高 1600Mbps, LPDDR3 支持最高     |  |

|                  |      | 1866Mbps。                            |  |

| DDR Controller   | 1    | 该 DDR 控制器支持单 rank 模式,最大支持 3GB        |  |

|                  |      | 内存容量,支持 64bit 数据位宽,同时支持 8bit ECC。    |  |

|                  |      | 该 DDR 控制器支持命令重排序、低功耗模式等              |  |

|                  |      | 功能,以提高系统性能。                          |  |

|                  |      | 芯片集成 1024KB 的片内 SRAM。该 SRAM 允许       |  |

| On Chip Memory   |      | 被片内所有主设备访问,可用作高带宽缓存。                 |  |

|                  |      | 芯片提供了3个DMA 控制器,每个DMA 控制              |  |

|                  |      | 器拥有8个DMA通道。                          |  |

| DMA              | 3    | 该控制器为基于列表项(Linked Lists)的分散/         |  |

|                  |      | 聚集型 DMA,支持地址递增/递减或无变化的传输方            |  |

|                  |      | 式。                                   |  |

|                  |      | 芯片包含1路Rapid IO 控制器 (内置PHY)。该控        |  |

|                  |      | 制器符合Rapid IO Gen2协议,最大支持4个Lane,支     |  |

|                  |      | 持最高5Gbps(BRC1)或6.25Gbps(BRC2)速率。     |  |

|                  |      | 该模块具有以下技术特征:                         |  |

|                  |      | ◆兼容RapidIO标准2.2版本;                   |  |

| RapidIO          |      | ◆支持1.25Gbaud, 2.5Gbaud, 3.125Gbaud及  |  |

|                  | 1    | 5Gbaud BRC1速率;                       |  |

|                  |      | ◆支持6.25Gbaud BRC2速率;                 |  |

|                  |      | ◆支持最高256 Byte数据负载;                   |  |

|                  |      | ◆支持34bit及50bitRIO寻址;                 |  |

|                  |      | ◆支持消息传送:数据及门铃信息;                     |  |

|                  |      | ◆支持DMA模式读写;                          |  |

| PCIe             | 1    | 芯片包含1路PCIe控制器(内置PHY),以进行PCI          |  |

| 模块名称       | 模块数量 | 模块功能                                     |  |

|------------|------|------------------------------------------|--|

|            |      | Express RC及EP应用。该控制器支持PCIe-Gen2 4通道      |  |

|            |      | 通信,具有如下技术特征:                             |  |

|            |      | ◆支持PCI Express Gen1及Gen2协议;              |  |

|            |      | ◆支持Gen2 (5.0 Gbps x 4 lanes);            |  |

|            |      | ◆支持128-bit内部数据深度,125MHz内部工作              |  |

|            |      | 频率;                                      |  |

|            |      | ◆支持ECRC生成及校验;                            |  |

|            |      | ◆支持RAS DES(Debug,Error injection,        |  |

|            |      | statistics);                             |  |

|            |      | ◆支持RAS DP (Data Protection),以对数据路径       |  |

|            |      | 及RAM进行校验;                                |  |

|            |      | ◆支持MSI (Message Signaled interrupt);     |  |

|            |      | ◆支持高级功耗及时钟管理                             |  |

|            |      | - 不支持D3 cold;                            |  |

|            |      | - 不支持L1 sub;                             |  |

|            |      | ◆可配置的BAR滤波器,I/O滤波器;                      |  |

|            |      | ◆嵌入式DMA(4读+4写通道)                         |  |

|            |      | ◆内置地址转换模块;                               |  |

|            |      | 该接口遵守 Camera Link v2.0 规范,实现数据接          |  |

|            |      | 收功能。                                     |  |

|            |      | ◆ 支持 Camera Link lite/base/medium/full/模 |  |

|            |      | 式;                                       |  |

|            |      | ◆ 支持 bit 分配;                             |  |

|            |      | ◆ 数据格式:                                  |  |

|            |      | - Mono 8/10/12/14/16;                    |  |

|            |      | - RAW 8/10/12/14/16;                     |  |

|            |      | - RGB 24/30/36;                          |  |

| CameraLink | 1    | ◆ Camera 控制信号:                           |  |

|            |      | - CC1: 脉冲或静态0/1信号;                       |  |

|            |      | - CC2: 脉冲或静态0/1信号;                       |  |

|            |      | - CC3: 脉冲或静态0/1信号;                       |  |

|            |      | - CC4: 脉冲或静态0/1信号;                       |  |

|            |      | ◆ 通信信号:                                  |  |

|            |      | - SerTFG:连接到UART RX;                     |  |

|            |      | - SerTC:连接到UART TX;                      |  |

|            |      | ◆ 通信波特率支持: 300bps 到 1500Kbps;            |  |

|            |      | ◆ 像素时钟范围: 20MHz 至 297MHz;                |  |

|            |      | 芯片集成 1 路 MIPI CSI-2 主控制器。该控制器用           |  |

| MIDI CCL 2 | 1    | 于接收 CSI-2 接口的摄像头传感器数据。同时芯片集              |  |

| MIPI CSI-2 |      | 成 MIPI-D PHY 模块。                         |  |

|            |      | ◆ 支持 MIPI 相关标准;                          |  |

| 模块名称     | 模块数量 | 模块功能                                              |  |

|----------|------|---------------------------------------------------|--|

|          |      | - MIPI Alliance Specification for Camera Serial   |  |

|          |      | Interface 2 (CSI-2), Version 1.2, January 2014    |  |

|          |      | - MIPI Alliance Specification for D-PHY, Version  |  |

|          |      | 1.2, September 2014                               |  |

|          |      | - MIPI Alliance Specification for C-PHY, Version  |  |

|          |      | 1.0, October 2014                                 |  |

|          |      | ◆ 高达 8 个 D-PHY RX 数据通道;                           |  |

|          |      | ◆ 每个 D-PHY 通道最高支持 2.5Gbps 通信速                     |  |

|          |      | 率;                                                |  |

|          |      | ◆ 每个 C-PHY 通道最高支持 2.5Gbps 通信速                     |  |

|          |      | 率;                                                |  |

|          |      | 芯片集成1路LVDS显示接口。该接口包含LVDS                          |  |

|          |      | 视频输出控制器及 LVDS TX 发送器。LVDS 视频输                     |  |

|          |      | 出控制器接收 DC8000 的视频输出数据,根据 VESA                     |  |

|          |      | (Video Electronics Standards Association)标准及      |  |

|          |      | JEIDA ( (Japanese Electronic Industry Development |  |

|          |      | Association)标准进行 LVDS 像素映射,并最终从                   |  |

|          |      | LVDS 发送器输出重映射后的并行数据。该 LVDS 控                      |  |

|          |      | 制器仅支持 FPD-Link 标准,不支持 FPD-Link II、                |  |

|          |      | FPD-Link III 及 V-By-One 标准。                       |  |

| LVDS     | 1    | ◆ 支持 LVDS 单通道输出 (4 lanes),最大并行                    |  |

|          |      | 数据宽度为 28 bit;                                     |  |

|          |      | ◆ 支持最大 150MHz 像素时钟及 LVDS 时钟;                      |  |

|          |      | ◆ 支持以下典型分辨率:                                      |  |

|          |      | - VGA(640x480)@60fps                              |  |

|          |      | - SVGA(800x600)@60fps                             |  |

|          |      | - XGA(1024x768)@60fps                             |  |

|          |      | - SXGA(1280x1024)@60fps                           |  |

|          |      | - UXGA(1600x1200)@60fps                           |  |

|          |      | - FHD(1920x1080)@60fps                            |  |

|          |      | 芯片集成1路SDIO3.0接口,该接口包括SDIO3.0                      |  |

| CDIO     | 1    | 控制器及 PHY 模块,支持安全数字存储器(SD                          |  |

| SDIO     | 1    | Mem),安全数字 I/O(SDIO)及多媒体卡(MMC)                     |  |

|          |      | 标准。                                               |  |

|          |      | 芯片包含1路千兆以太网控制器GMAC,与片外                            |  |

|          |      | 以太网PHY配合使用。                                       |  |

|          |      | 该模块具有以下特征:                                        |  |

| Ethernet | 1    | ◆ 支持GMII/RGMII接口;                                 |  |

|          |      | ◆ 支持10,100及1000Mbps数据传输率;                         |  |

|          |      | ◆ GMAC支持全双工及半全双工操作;                               |  |

|          |      | ◆ GMAC支持帧滤波操作;                                    |  |

| 模块名称                  | 模块数量 | 模块功能                        |  |

|-----------------------|------|-----------------------------|--|

|                       |      | ◆ 支持硬件校验核计算及纠错;             |  |

|                       |      | 芯片集成1路外部存储器接口控制器,用以读写       |  |

|                       |      | 片外异步 SRAM 或并行 NOR flash。    |  |

|                       |      | 该控制器具有以下特征:                 |  |

|                       |      | ◆ 支持8bit及16bit数据位宽;         |  |

| EMI Controller        | 1    | ◆ 支持 4 个地址片选信号,每个分配 32MB 地  |  |

|                       |      | 址空间;                        |  |

|                       |      | ◆ 支持 CPU 模式及 DMA 模式;        |  |

|                       |      | ◆ 可编程异步读写时间;                |  |

|                       |      | ◆ 支持地址/数据复用及页模式;            |  |

|                       |      | NAND FLASH控制器模块包含控制器和PHY。该  |  |

|                       |      | 模块提供丰富的功能,以最大化系统级性能,并提供     |  |

|                       |      | 功能最丰富和最灵活的NAND闪存解决方案,支持企    |  |

|                       |      | 业级存储和嵌入式内存应用程序。             |  |

|                       |      | ◆ 支持4个片选信号,支持1~8个地址周期,      |  |

|                       |      | 无最大容量限制;                    |  |

|                       |      | ◆ 支持8/16 bit Flash IO总线位宽;  |  |

|                       |      | ◆ 支持512KB, 2KB, 4KB及8KB页尺寸, |  |

|                       |      | SLC/MLC NAND flash设备;       |  |

| Nand Flash Controller | .1   | ◆ 支持8/16 bit Flash IO总线位宽;  |  |

| Nand Flash Controller |      | ◆ 支持大部分主流flash器件命令;提供Up模式   |  |

|                       |      | 以用于特殊命令的flash接口操作;          |  |

|                       |      | ◆ 支持双平面操作;                  |  |

|                       |      | ◆ 支持8/16 bit Flash IO总线位宽;  |  |

|                       |      | ◆ 自动在线、片内缓存错误纠正;内部ECC电      |  |

|                       |      | 路能够纠正每512B数据中最多8或15比特随机错误,  |  |

|                       |      | 或每1024B数据中最多24或40或60比特随机错误。 |  |

|                       |      | ◆ 支持DMA操作;                  |  |

|                       |      | ◆ 支持数据保护模式;                 |  |

|                       |      | ◆ 可编程R/W脉冲时序;               |  |

|                       |      | 芯片具有2路USB2.0接口。其中一路支持主机和    |  |

|                       |      | 从机功能,完全兼容USB2.0协议。另一路接口支持非  |  |

|                       |      | OTG主模式。该模块主要性能特征如下:         |  |

|                       |      | ◆ 软件可配置为OTG1.3或OTG2.0操作模式;  |  |

|                       |      | ◆ 支持以下速度:                   |  |

| USB2.0                | 2    | 高速(HS,480-Mbps);            |  |

|                       |      | 全速 (FS, 12-Mbps);           |  |

|                       |      | 低速(LS,1.5-Mbps)模式;          |  |

|                       |      | ◆ 支持多达7个双向端点,包括控制端点0;       |  |

|                       |      | ◆ 支持多达14个主通道;               |  |

|                       |      | ◆ 支持SRP协议及HNP协议;            |  |

| 模块名称   | 模块数量 | 模块功能                                                                                |  |

|--------|------|-------------------------------------------------------------------------------------|--|

|        |      | ◆ 集成内部DMA;                                                                          |  |

|        |      | QSPI模块可做为串行主设备使用。该模块主要性                                                             |  |

|        |      | 能特征如下:                                                                              |  |

|        |      | ◆ 支持DMA传输模式;                                                                        |  |

| O GPV  |      | ◆ 支持最高50MHz速率;                                                                      |  |

| QSPI   | 1    | ◆ 支持4种SPI操作模式;                                                                      |  |

|        |      | ◆ 支持全双工模式;                                                                          |  |

|        |      | ◆ 可编程MSB或LSB;                                                                       |  |

|        |      | ◆ 支持最多2个外部从设备;                                                                      |  |

|        |      | 芯片提供了2路SPI(SPI0-SPI1)接口,2个SPI                                                       |  |

|        |      | 控制器的结构和功能完全相同。可以配置为spi主控设                                                           |  |

|        | _    | 备(master)或者配置为spi从设备(slave)。发送字                                                     |  |

| SPI    | 2    | 长、位顺序、等都可以配置。模块主要由发送/接收                                                             |  |

|        |      | FIFO、主控制器、从设备控制器、时钟产生模块及同                                                           |  |

|        |      | 步逻辑组成。该模块最高支持50MHz传输速率。                                                             |  |

|        |      | 芯片提供了4路UART接口,其中一个支持流量控                                                             |  |

|        |      | 制功能。                                                                                |  |

|        |      | 该模块具备如下性能特征:                                                                        |  |

| UART   | 4    | ◆ 收发FIFO深度为16;                                                                      |  |

|        |      | ◆ 可编程的帧长度,奇偶校验及停止位长度可                                                               |  |

|        |      | 配置;                                                                                 |  |

|        |      | ◆ 波特率可配置;                                                                           |  |

|        |      | 芯片内部集成4路32位定时器。该定时器具有如                                                              |  |

|        |      | 下性能特征:                                                                              |  |

|        |      | ◆ 三种计数模式:自由运行,周期计数,单次                                                               |  |

| Timer  | 4    | 计数;                                                                                 |  |

|        |      | ◆ 4个独立32bit递减计数器;                                                                   |  |

|        |      | ◆ 4个独立中断信号;                                                                         |  |

|        |      | ◆ 4组输入时钟捕捉管脚;                                                                       |  |

|        |      | RTC可用于提供基本的报警功能或作为计数器                                                               |  |

|        |      | 使用。该模块具有以下技术特征:                                                                     |  |

|        |      | ◆ 支持年/日/小时/分/秒/毫秒;                                                                  |  |

| RTC    | 1    | ◆ 支持时间精度补偿;                                                                         |  |

|        |      | ◆ 支持定时值初始化;                                                                         |  |

|        |      | ◆ 25℃下日时间偏差为1s;                                                                     |  |

|        |      | ◆ 支持时间报警功能;                                                                         |  |

|        |      | 芯片提供了4个I <sup>2</sup> C(I <sup>2</sup> C0- I <sup>2</sup> C3)接口,4个I <sup>2</sup> C控 |  |

| 1,20   | _    | 制器的结构和功能完全相同。提供标准模式,快速模                                                             |  |

| $I^2C$ | 4    | 式,高速模式三种不同的工作模式,支持7位或10位                                                            |  |

|        |      | 寻址,支持主从模式。                                                                          |  |

| $I^2S$ | 1    | 芯片内集成了I <sup>2</sup> S音频数据传输处理模块。该模块                                                |  |

| 模块名称            | 模块数量 | 模块功能                                                  |

|-----------------|------|-------------------------------------------------------|

|                 |      | 是4线接口(WS, SCLK, SD_IN, SD_OUT), 支持                    |

|                 |      | 标准I <sup>2</sup> S协议。该芯片的I <sup>2</sup> S最大支持24位数据位宽的 |

|                 |      | 数据传输且只能作为主机使用。                                        |

|                 |      | 芯片内部集成一通道的1553B总线控制器,支持                               |

| 1552D           | 1    | BC、RT 和BM 三种工作模式,支持完整的                                |

| 1553B           | 1    | MIL-STD-1553B协议,数据传输速率1Mbps和10Mbps                    |

|                 |      | 可配置,存储器布局和寄存器设置同BU-61580兼容。                           |

|                 |      | GPIO模块特性如下:                                           |

|                 |      | ◆ 包含64个独立可配置GPIO信号;                                   |

|                 |      | ◆ 每个信号分别由数据寄存器和数据方向寄                                  |

| GPIO            | 1    | 存器对应位控制;                                              |

|                 |      | ◆ GPIO[31:0]支持外部中断触发;                                 |

|                 |      | ◆ 中断支持上升沿/下降沿/高电平/低电平四种                               |

|                 |      | 触发模式。                                                 |

|                 |      | 芯片包含2路CAN总线控制器。该控制器兼容                                 |

| CAN             | 2    | CAN 2.0B协议,支持BasicCAN和PeliCAN模式,这两                    |

| CAN             | 2    | 种模式可以通过时钟分频寄存器选择。在BasicCAN                            |

|                 |      | 和PeliCAN两种模式下寄存器的映射有所不同。                              |

|                 |      | 芯片集成SM4硬件加密模块,具有以下技术特                                 |

|                 |      | 征:                                                    |

|                 |      | ◆ 支持SM4加、解密功能;                                        |

|                 |      | ◆ 支持以下几种模式:                                           |

| SM4             | 1    | - ECB (Electronic codebook);                          |

|                 |      | - CBC (Cipher-block chaining);                        |

|                 |      | - CFG (Cipher feedback);                              |

|                 |      | - OFB (Output feedback);                              |

|                 |      | - CTR (Counter mode).                                 |

|                 |      | 芯片集成逐次逼近式模数转换器(SAR ADC)。                              |

|                 |      | 该ADC为12位采样精度,支持1MSPS的低速模式或                            |

|                 |      | 5MSPS的高速模式。                                           |

| SAR ADC         | 1    | ◆ DNL: +/-1.5 LSB, INL: +/-3 LSB;                     |

|                 |      | ◆ 数据率: 1MSPS/5MSPS;                                   |

|                 |      | ◆ 模拟输入范围: VREFH到VREFL;                                |

|                 |      | ◆ 2通道单端或差分模拟输入。                                       |

| EFUSE memory    | 1    | 128 Byte Efuse 控制器及存储单元。                              |

| Bootrom for ARM | 1    | 该模块存储片内固化的ARM Bootloader程序。                           |

|                 |      | 芯片内部集成看门狗模块,看门狗模块由一个16                                |

| TT . 1 1        |      | 位向下计数器组成,具有可编程超时间隔,能够在超                               |

| Watchdog        | 1    | 时时产生中断和复位信号,可以用于在系统出现故障                               |

|                 |      | 时,对芯片进行复位。                                            |

| PVT sensor      | 1    | 芯片集成电压、温度传感器,用以采集芯片电压、                                |

| 模块名称 | 模块数量 | 模块功能  |

|------|------|-------|

|      |      | 温度信息。 |

# 2. 封装和信号定义

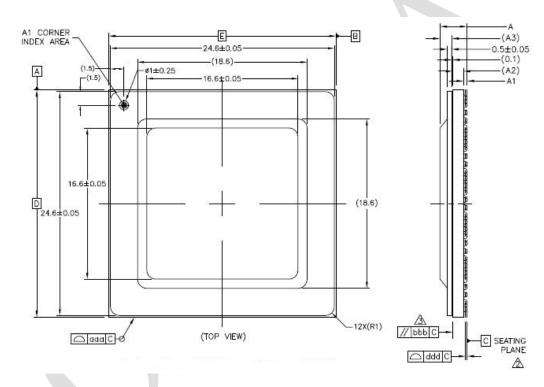

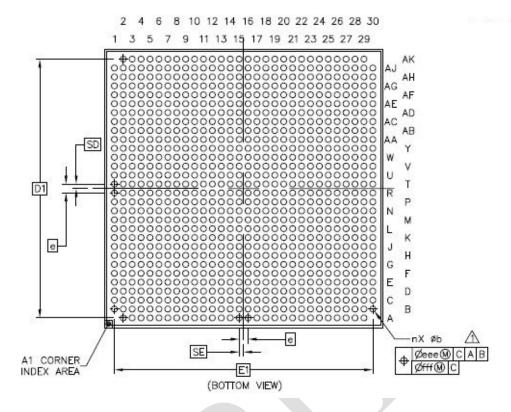

## 2.1 封装信息

- ▶ 封装形式为 FCBGA896, Package size 为 25mm\*25mm, Ball pitch 为 0.8 mm;

- ▶ 其外形如图 2-1, 2-2 所示;

- ▶ 表 2-1 为封装尺寸说明。

图 2-1Yulong810A 芯片 FCBGA896 封装外形图

AEROSPACE 欧比特

#### 图 2-2 FCBGA896 封装外形图

#### 表 2-1 FCBGA896 封装尺寸说明

| 表 2-1 FCBGA650 到表/(1) 阮明 |      |      |      |  |

|--------------------------|------|------|------|--|

| 符号                       | 最小值  | 典型值  | 最大值  |  |

| A                        |      |      | 3.18 |  |

| A1                       | 0.36 |      | 0.46 |  |

| A2                       |      | 1.17 | REF  |  |

| A3                       |      | 1.3  | REF  |  |

| D                        |      | 25   | BSC  |  |

| E                        |      | 25   | BSC  |  |

| b                        | 0.44 |      | 0.64 |  |

| e                        |      | 0.8  | BSC  |  |

| n                        |      | 896  |      |  |

| D1                       |      | 23.2 | BSC  |  |

| E1  | 23.2 | BSC |

|-----|------|-----|

| SD  | 0.4  | BSC |

| SE  | 0.4  | BSC |

| aaa | 0.15 |     |

| bbb | 0.25 |     |

| ddd | 0.2  |     |

| eee | 0.25 |     |

| fff | 0.1  |     |

注:尺寸数据单位:毫米

# 2.2 封装信号引脚定义

表 2-2 芯片引脚信号表

|            |     | 秋とと心バリル    | PILL DIV                 |     |          |

|------------|-----|------------|--------------------------|-----|----------|

| 类别         | 引脚号 | 引脚名及复用     | 功能描述                     | I/O | 引脚<br>电平 |

|            | D26 | TEST_MODE  | 测试模式,高有效                 | I   |          |

| G1 1 1     | F25 | BOOT_SEL0  | 0: A9 活动, 1: A9 活动       | I   |          |

| Global (5) | E24 | BOOT_SEL1  | 保留,输入高                   | I   |          |

|            | D25 | BOOT_SEL2  | 0: ROM boot, 1: EMI boot | I   |          |

|            | D24 | RESETN     | 芯片复位,低有效                 | I   |          |

|            |     | UART0_RXD* | UART0 接收                 |     |          |

|            | F24 | I2C3_SCL   | I2C 3 时钟                 | I/O |          |

| UART-0     |     | 2ND_GPIO33 | 第 2 组 GPIO33             |     |          |

| (2)        | F23 | UART0_TXD* | UART0 发送                 |     |          |

|            |     | I2C3_SDA   | I <sup>2</sup> C 3 数据    | I/O |          |

|            |     | 2ND_GPIO34 | 第 2 组 GPIO34             |     |          |

|            |     | UART1_RXD* | UART1 接收                 |     |          |

|            | E23 | CAN1_RXD   | CAN1 接收                  | I/O |          |

| UART-1     |     | 2ND_GPIO35 | 第 2 组 GPIO35             |     |          |

| (2)        |     | UART1_TXD* | UART1 发送                 |     |          |

|            | D23 | CAN1_TXD   | CAN1 发送                  | I/O |          |

|            |     | 2ND_GPIO36 | 第 2 组 GPIO36             |     |          |

| UART-2     | E22 | UART2_RXD* | UART2 接收                 | I/O |          |

| (2)       |       | SPI1 SCLK   | SPI1 时钟              |      |

|-----------|-------|-------------|----------------------|------|

|           |       | 2ND_GPIO37  | 第 2 组 GPIO37         |      |

|           |       | UART2_TXD*  | UART2 发送             |      |

|           | D22   | SPI1_CSN0   | SPI1 片选              | I/O  |

|           |       | 2ND_GPIO38  | 第 2 组 GPIO38         |      |

|           |       | UART3_RXD*  | UART3 接收             |      |

|           | F22   | SPI1_MISO   | SPI1 主入从出            | I/O  |

| UART-3    |       | 2ND_GPIO39  | 第 2 组 GPIO39         |      |

| (2)       |       | UART3_TXD*  | UART3 发送             |      |

|           | F21   | SPI1_MOSI   | SPI1 主出从入            | I/O  |

|           |       | 2ND_GPIO40  | 第 2 组 GPIO40         |      |

|           |       | I2C0_SCL*   | I <sup>2</sup> C0 时钟 |      |

|           | A12   | 2ND_GPIO41  | 定时器 0 输入信号           | I/O  |

| I2C-0     |       | TIMER IN0   | 第 2 组 GPIO41         |      |

| (2)       |       | I2C0 SDA*   | I <sup>2</sup> C0 数据 |      |

|           | A13   | 2ND GPIO42  | 第 2 组 GPIO42         | I/O  |

|           |       | TIMER IN1   | 定时器 1 输入信号           | 7    |

|           |       | I2C1 SCL*   | I <sup>2</sup> C1 时钟 |      |

|           | A11   | UART0_CTSn  | UART0 发送允许           | I/O  |

| I2C-1     |       | TRACECLK    | A9 trace port clk 信号 |      |

| (2)       |       | I2C1 SDA*   | I <sup>2</sup> C1 数据 |      |

|           | B11   | UARTO RTSn  | UART 发送请求            | I/O  |

|           |       | TRACECTL    | A9 trace port ctl 信号 | 7    |

|           |       | SPI0 SCLK*  | SPI0 时钟              | 1_,_ |

|           | D20   | 2ND GPIO43  | 第 2 组 GPIO43         | I/O  |

| =         |       | SPI0 CSN*   | SPI0 片选              | 7/0  |

| SPI-0 (4) | D21 - | 2ND GPIO44  | 第 2 组 GPIO44         | I/O  |

| 5110(1)   | 7.00  | SPI0 MISO*  | SPI0 主入从出            | 7/0  |

|           | E20   | 2ND GPIO45  | 第 2 组 GPIO45         | I/O  |

| F         | FILE  | SPI0_MOSI*  | SPI0 主出从入            | 1/0  |

|           | F19   | 2ND_GPIO46  | 第 2 组 GPIO46         | I/O  |

|           | F2.0  | QXHW_CLK*   | 1553B 时钟             | 1/0  |

|           | F20   | 2ND_GPIO47  | 第 2 组 GPIO47         | I/O  |

| ŀ         | F10   | QXHW_RXA*   | 1553B 通道 A 接收        | 1/0  |

| OMINA     | E19 – | 2ND_GPIO48  | 第 2 组 GPIO48         | I/O  |

| QXHW      | D10   | QXHW_RXA_N* | 1553B 通道 A 接收        | 1/0  |

| (11)      | D19   | 2ND_GPIO49  | 第 2 组 GPIO49         | I/O  |

| ļ         | E10   | QXHW_RXB*   | 1553B 通道 B 接收        | T/C  |

|           | E18   | 2ND_GPIO50  | 第 2 组 GPIO50         | I/O  |

| ļ         | D10   | QXHW RXB N* | 1553B 通道 B 接收        | 1/0  |

|           | D18   | 2ND GPIO51  | 第 2 组 GPIO51         | I/O  |

|          | E10   | QXHW_TXA*     | 1553B 通道 A 发送        | I/O      |

|----------|-------|---------------|----------------------|----------|

|          | F18   | 2ND_GPIO52    | 第 2 组 GPIO52         |          |

|          | F17   | QXHW_TXA_N*   | 1553B 通道 A 发送        | I/O      |

|          | E17   | 2ND_GPIO53    | 第 2 组 GPIO53         | I/O      |

|          | D17 — | QXHW_TXA_INH* | 1553B 通道 A 发送禁止      | I/O      |

|          |       | 2ND_GPIO54    | 第 2 组 GPIO54         | I/O      |

|          |       | QXHW_TXB*     | 1553B 通道 B 发送        | I/O      |

|          |       | 2ND_GPIO55    | 第 2 组 GPIO55         | I/O      |

| <u> </u> | D16   | QXHW_TXB_N*   | 1553B 通道 B 发送        | I/O      |

|          | D16   | 2ND_GPIO56    | 第 2 组 GPIO56         | I/O      |

|          | F1.6  | QXHW_TXB_INH* | 1553B 通道 B 发送禁止      | I/O      |

|          | F16   | 2ND_GPIO57    | 第2组 GPIO57           | I/O      |

|          | E10   | QSPI_SCLK*    | QSPI 时钟              | 1/0      |

|          | E12   | 2ND_GPIO58    | 第 2 组 GPIO58         | I/O      |

| Ī        | -10   | QSPI CSN0*    | QSPI 片选              | 7.10     |

|          | F10   | 2ND GPIO59    | 第 2 组 GPIO59         | I/O      |

| =        |       | QSPI MOSI*    | QSPI 主出从入信号          | 7/0      |

| QSPI (6) | D12   | 2ND GPIO60    | 第 2 组 GPIO60         | I/O      |

| Q211(0)  | F12   | QSPI MISO*    | QSPI 主入从出信号          |          |

|          |       | 2ND GPIO61    | 第 2 组 GPIO61         | I/O      |

| Ī        | D11   | QSPI WPN*     | QSPI 写保护             | 7/0      |

|          |       | 2ND GPIO62    | 第 2 组 GPIO62         | I/O      |

| =        | E11 - | QSPI HOLDN*   | QSPI 保持信号            | 7/0      |

|          |       | 2ND GPIO63    | 第 2 组 GPIO63         | I/O      |

|          | C15   | I2S SCLK*     | I2S 位时钟输出            | 7/0      |

|          |       | I2C2 SCL      | I <sup>2</sup> C2 时钟 | I/O      |

| =        | A15   | I2S LRCK*     | I2S 帧时钟输出            |          |

| I2S (4)  |       | I2C2 SDA      | I <sup>2</sup> C2 数据 | I/O      |

| 125 (1)  |       | I2S SDI*      | I2S 输入信号             |          |

|          | B14   | PWM OUT0      | PWM 信号输出 0           | I/O      |

| =        |       | I2S SDO*      | I2S 输出信号             |          |

|          | A14   | PWM OUT1      | PWM 信号输出 1           | I/O      |

|          |       | CAN0 RXD*     | CAN0 总线接收            |          |

|          | B13   | NF CE[2]      | NAND FLASH 片选 2      | I/O      |

| CAN-0    |       | EMI UBN       |                      |          |

| (2)      |       | CAN0 TXD*     | CAN0 总线发送            |          |

|          | C13   | NF CE[3]      | NAND FLASH 片选 3      | О        |

|          |       | EMI LBN       | 未知                   | $\dashv$ |

|          |       | GPIO PIN0*    | 第一组 GPIO0            |          |

| GPIO (8) | E15   | EXT IRQ0      | 外部中断 0               | I/O      |

|          | E15   |               |                      |          |

|       |      |                    | 0x0: UART;                        |     |  |

|-------|------|--------------------|-----------------------------------|-----|--|

|       |      |                    | 0x1: SD Card;                     |     |  |

|       |      |                    | 0x2: eMMC Card;                   |     |  |

|       |      |                    | 0x3: QSPI Nor Flash;              |     |  |

|       |      |                    | 0x4: Nand Flash;                  |     |  |

|       |      |                    | 0x5-0xFF: 保留;                     |     |  |

|       |      | GPIO_PIN1*         | 第一组 GPIO1                         |     |  |

|       | D15  | EXT_IRQ1           | 外部中断 1                            | I/O |  |

|       |      | BOOT_2ND[1]        | 参考 BOOT_2ND[0]                    |     |  |

|       |      | GPIO_PIN2*         | 第一组 GPIO2                         |     |  |

|       | C14  | EXT_IRQ2           | 外部中断 2                            | I/O |  |

|       |      | BOOT 2ND[2]        | 参考 BOOT 2ND[0]                    |     |  |

|       |      | GPIO PIN3*         | 第一组 GPIO3                         |     |  |

|       | D14  | EXT IRQ3           | 外部中断 3                            | I/O |  |

|       |      | BOOT 2ND[3]        | 参考 BOOT 2ND[0]                    |     |  |

|       |      | GPIO PIN4*         | 第一组 GPIO4                         |     |  |

|       | E14  | WDT OUT            | 芯片看门狗复位输出信号                       | I/O |  |

|       |      | BOOT 2ND[4]        | 参考 BOOT 2ND[0]                    |     |  |

|       |      | GPIO PIN5*         | 第一组 GPIO5                         |     |  |

|       | F14  | QSPI CSN1          | QSPI 片选 1                         | I/O |  |

|       |      | BOOT 2ND[5]        | 参考 BOOT 2ND[0]                    |     |  |

|       |      | GPIO PIN6*         | 第一组 GPIO6                         |     |  |

|       | E13  | SPI0 CSN1          | SPI0 片选 1                         | I/O |  |

|       |      | BOOT 2ND[6]        | 参考 BOOT 2ND[0]                    |     |  |

|       |      | GPIO PIN7*         | 第一组 GPIO7                         |     |  |

|       | D13  | SPI1 CSN1          | SPI1 片选 1                         | I/O |  |

|       |      | BOOT 2ND[7]        | 参考 BOOT 2ND[0]                    |     |  |

|       |      | NF CEN0*           | Nand flash 片选信号 0                 |     |  |

|       | B10  | GPIO PIN8          | 第一组 GPIO8                         | I/O |  |

|       |      | TRACE0             | A9 trace 信号 0                     |     |  |

|       |      | NF_CEN1*           | Nand flash 片选信号 1                 |     |  |

|       | C10  | GPIO_PIN9          | 第一组 GPIO9                         | I/O |  |

| NAND  |      | TRACE1             | A9 trace 信号 1                     |     |  |

| FLASH |      | NF_ALE*            | Nand flash 地址锁存使能信号               |     |  |

|       | A10  | GPIO PIN10         | 第一组 GPIO10                        | I/O |  |

| (16)  | 1110 | TRACE2             | A9 trace 信号 2                     |     |  |

|       |      |                    | <del> </del>                      |     |  |

|       |      | NF_CLE*            | Nand flash 命令锁存使能信号               |     |  |

| ļ ļ   | D10  | NF_CLE* GPIO_PIN11 | Nand flash 命令锁存使能信号<br>第一组 GPIO11 | I/O |  |

|       | D10  |                    |                                   | I/O |  |

|       | D10  | GPIO_PIN11         | 第一组 GPIO11                        | I/O |  |

|          |     | TRACE4             | A9 trace 信号 4     |     |  |

|----------|-----|--------------------|-------------------|-----|--|

|          |     | NF_WEN*            | Nand flash 写信号    |     |  |

|          | C11 | GPIO_PIN13         | 第一组 GPIO13        | I/O |  |

|          |     | TRACE5             | A9 trace 信号 5     |     |  |

|          |     | NF_WPN*            | Nand flash 写保护信号  |     |  |

|          | A9  | GPIO_PIN14         | 第一组 GPIO14        | I/O |  |

|          |     | TRACE6             | A9 trace 信号 6     |     |  |

|          |     | NF_RBN*            | Nand flash 忙状态信号  |     |  |

|          | E9  | GPIO_PIN15         | 第一组 GPIO15        | I/O |  |

|          |     | TRACE7             | A9 trace 信号 7     |     |  |

|          |     | NF_IO0*            | Nand flash 数据信号 0 |     |  |

|          | C9  | GPIO_PIN16         | 第一组 GPIO16        | I/O |  |

|          |     | TRACE8             | A9 trace 信号 8     |     |  |

|          |     | NF_IO1*            | Nand flash 数据信号 1 |     |  |

|          | D9  | GPIO_PIN17         | 第一组 GPIO17        | I/O |  |

|          |     | TRACE9             | A9 trace 信号 9     |     |  |

|          |     | NF_IO2*            | Nand flash 数据信号 2 |     |  |

|          | F8  | GPIO_PIN18         | 第一组 GPIO18        | I/O |  |

|          |     | TRACE10            | A9 trace 信号 10    |     |  |

| -        |     | NF_IO3*            | Nand flash 数据信号 3 |     |  |

|          | F7  | GPIO_PIN19         | 第一组 GPIO19        | I/O |  |

|          |     | TRACE11            | A9 trace 信号 11    |     |  |

|          |     | NF_IO4*            | Nand flash 数据信号 4 |     |  |

|          | E8  | GPIO_PIN20         | 第一组 GPIO20        | I/O |  |

|          |     | TRACE12            | A9 trace 信号 12    |     |  |

|          |     | NF_IO5*            | Nand flash 数据信号 5 |     |  |

|          | D8  | GPIO_PIN21         | 第一组 GPIO21        | I/O |  |

|          |     | TRACE13            | A9 trace 信号 13    |     |  |

|          |     | NF_IO6*            | Nand flash 数据信号 6 |     |  |

|          | C8  | GPIO_PIN22         | 第一组 GPIO22        | I/O |  |

|          |     | TRACE14            | A9 trace 信号 14    |     |  |

|          |     | NF_IO7*            | Nand flash 数据信号 7 |     |  |

|          | B8  | GPIO_PIN23         | 第一组 GPIO23        | I/O |  |

|          |     | TRACE15            | A9 trace 信号 15    |     |  |

| USB-0    | C12 | USB0_VBUS_VLDEN*   |                   | 0   |  |

| USB-0    | C12 | SDIO_VOLT_EN       |                   | 701 |  |

|          | A7  | SDIO_RESET_N*      | 设备复位信号输出          | О   |  |

| SDIO (3) | A8  | SDIO_CARD_DETECT_N | 卡发现信号,低为与卡连接      | I   |  |

|          | В7  | SDIO_WRITE_PROTECT | 写保护信号,低为写保护       | I   |  |

| EMI (51) | G2  | EMI_CSN0*          | EMI 片选 0          | 1/0 |  |

| `        | G2  | GPIO_PIN24         | 第一组 GPIO24        | I/O |  |

|          |     |                    |                   |     |  |

|   | F5   | EMI_CSN1*  | EMI 片选 1           | I/O |

|---|------|------------|--------------------|-----|

|   | гэ   | GPIO_PIN25 | 第一组 GPIO25         |     |

|   | ΕO   | EMI_CSN2*  | EMI 片选 2           | I/O |

|   | F2   | GPIO_PIN26 | 第一组 GPIO26         |     |

| - | Г1   | EMI_CSN3*  | EMI 片选 3           | I/O |

|   | F1   | GPIO_PIN27 | 第一组 GPIO27         | I/O |

| Ī | C.4  | EMI_OEN*   | EMI 输出使能           | I/O |

|   | G4   | GPIO_PIN28 | 第一组 GPIO28         | I/O |

| = | C2   | EMI_WEN*   | EMI 写信号            | I/O |

|   | G3   | GPIO_PIN29 | 第一组 GPIO29         | I/O |

| Ī | 116  | EMI_WAIT0* |                    | I/O |

|   | Н6   | GPIO_PIN30 | 第一组 GPIO30         | I/O |

| Ī | 11.5 | EMI_WAIT1* |                    | 1/0 |

|   | Н5   | GPIO_PIN31 | 第一组 GPIO31         | I/O |

|   | 00   | EMI_WAIT2* |                    | I/O |

|   | G6   | GPIO_PIN32 | 第一组 GPIO32         | I/O |

|   | 05   | EMI_WAIT3* |                    | I/O |

|   | G5   | GPIO_PIN33 | 第一组 GPIO33         | I/O |

|   | C1   | EMI_DQ0*   | EMI 数据 0           | I/O |

|   | G1   | GPIO_PIN34 | 第一组 GPIO34         | I/O |

|   | H1   | EMI_DQ1*   | EMI 数据 1           | I/O |

|   | ні   | GPIO_PIN35 | 第一组 GPIO35         |     |

|   | Н2   | EMI_DQ2*   | EMI 数据 2           | I/O |

|   | П2   | GPIO_PIN36 | 第一组 GPIO36         |     |

|   | НЗ   | EMI_DQ3*   | EMI 数据 3           | I/O |

|   | ПЭ   | GPIO_PIN37 | 第一组 GPIO37         |     |

|   | H4   | EMI_DQ4*   | EMI 数据 4           | I/O |

|   | 114  | GPIO_PIN38 | 第一组 GPIO38         |     |

|   | J5   | EMI_DQ5*   | EMI 数据 5           | I/O |

|   | 33   | GPIO_PIN39 | 第一组 GPIO39         | 1/0 |

|   | J5   | EMI_DQ6*   | EMI 数据 6           | I/O |

|   | 3.5  | GPIO_PIN40 | 第一组 GPIO40         | 1/0 |

|   | J2   | EMI_DQ7*   | EMI 数据 7           | I/O |

|   | 32   | GPIO_PIN41 | 第一组 GPIO41         | 1/0 |

|   | J1   | EMI_DQ8*   | EMI 数据 8           | I/O |

|   | 31   | NF_IO[8]   | Nand flash 数据信号 8  | 1/0 |

|   | K1   | EMI_DQ9*   | EMI 数据 9           | I/O |

|   | 17.1 | NF_IO[9]   | Nand flash 数据信号 9  |     |

|   | K2   | EMI_DQ10*  | EMI 数据 10          | I/O |

|   | 114  | NF_IO[10]  | Nand flash 数据信号 10 |     |

|   | K3   | EMI_DQ11*  | EMI 数据 11          | I/O |

|      | NF_IO[11]                             | Nand flash 数据信号 11                    |     |  |

|------|---------------------------------------|---------------------------------------|-----|--|

| 17.4 | EMI_DQ12*                             | EMI 数据 12                             | I/O |  |

| K4   | NF_IO[12]                             | Nand flash 数据信号 12                    | I/O |  |

| 17.5 | EMI_DQ13*                             | EMI 数据 13                             | 1/0 |  |

| K5   | NF_IO[13]                             | Nand flash 数据信号 13                    | I/O |  |

| 17.6 | EMI_DQ14*                             | EMI 数据 14                             | 1/0 |  |

| K6   | NF_IO[14]                             | Nand flash 数据信号 14                    | I/O |  |

| Ι.(  | EMI_DQ15*                             | EMI 数据 15                             | I/O |  |

| L6   | NF_IO[15]                             | Nand flash 数据信号 15                    | I/O |  |

|      | EMI_A0*                               | EMI 地址 0                              |     |  |

| L5   | GPIO_PIN42                            | 第一组 GPIO42                            | I/O |  |

|      | BT1120_CLK                            | BT1120 时钟                             |     |  |

|      | EMI_A1*                               | EMI 地址 1                              |     |  |

| L4   | GPIO_PIN43                            | 第一组 GPIO43                            | I/O |  |

|      | BT1120_D15                            | BT1120 数据 15                          |     |  |

|      | EMI_A2*                               | EMI 地址 2                              |     |  |

| L3   | GPIO_PIN44                            | 第一组 GPIO44                            | I/O |  |

|      | BT1120_D14                            | BT1120 数据 14                          |     |  |

|      | EMI_A3*                               | EMI 地址 3                              |     |  |

| L2   | GPIO_PIN45                            | 第一组 GPIO45                            | I/O |  |

|      | BT1120_D13                            | BT1120 数据 13                          |     |  |

|      | EMI_A4*                               | EMI 地址 4                              |     |  |

| M2   | GPIO_PIN46                            | 第一组 GPIO46                            | I/O |  |

|      | BT1120_D12                            | BT1120 数据 12                          |     |  |

|      | EMI_A5*                               | EMI 地址 5                              |     |  |

| M3   | GPIO_PIN47                            | 第一组 GPIO47                            | I/O |  |

|      | BT1120_D11                            | BT1120 数据 11                          |     |  |

|      | EMI_A6*                               | EMI 地址 6                              |     |  |

| M4   | GPIO_PIN48                            | 第一组 GPIO48                            | I/O |  |

|      | BT1120_D10                            | BT1120 数据 10                          |     |  |

|      | EMI_A7*                               | EMI 地址 7                              |     |  |

| M5   | GPIO_PIN49                            | 第一组 GPIO49                            | I/O |  |

|      | BT1120_D9                             | BT1120 数据 9                           |     |  |

|      | EMI_A8*                               | EMI 地址 8                              |     |  |

| M6   | GPIO_PIN50                            | 第一组 GPIO50                            | I/O |  |

|      | BT1120_D8                             | BT1120 数据 8                           |     |  |

|      | EMI_A9*                               | EMI 地址 9                              |     |  |

| N5   | GPIO_PIN51                            | 第一组 GPIO51                            | I/O |  |

|      | BT1120_D7                             | BT1120 数据 7                           |     |  |

| N4   | EMI_A10*                              | EMI 地址 10                             | I/O |  |

| 114  | GPIO_PIN52                            | 第一组 GPIO52                            | 1/0 |  |

| <br> | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |     |  |

|        |            | BT1120_D6    | BT1120 数据 6    |     |

|--------|------------|--------------|----------------|-----|

|        |            | EMI_A11*     | EMI 地址 11      |     |

|        | N3         | GPIO PIN53   | 第一组 GPIO53     | I/O |

|        |            | BT1120 D5    | BT1120 数据 5    |     |

|        |            | EMI A12*     | EMI 地址 12      |     |

|        | P4         | GPIO PIN54   | 第一组 GPIO54     | I/O |

|        |            | BT1120 D4    | BT1120 数据 4    |     |

|        |            | EMI A13*     | EMI 地址 13      |     |

|        | P5         | GPIO PIN55   | 第一组 GPIO55     | I/O |

|        |            | BT1120 D3    | BT1120 数据 3    |     |

|        |            | EMI A14*     | EMI 地址 14      |     |

|        | P6         | GPIO PIN56   | 第一组 GPIO56     | I/O |

|        |            | BT1120 D2    | BT1120 数据 2    |     |

|        |            | EMI A15*     | EMI 地址 15      |     |

|        | R5         | GPIO PIN57   | 第一组 GPIO57     | I/O |

|        |            | BT1120 D1    | BT1120 数据 1    |     |

|        |            | EMI A16*     | EMI 地址 16      |     |

|        | R4         | GPIO PIN58   | 第一组 GPIO58     | I/O |

|        |            | BT1120 D0    | BT1120 数据 0    |     |

|        |            | EMI A17*     | EMI 地址 17      |     |

|        | T4         | GPIO PIN59   | 第一组 GPIO59     | I/O |

|        |            | EMI A18*     | EMI 地址 18      |     |

|        | T5         | GPIO PIN60   | 第一组 GPIO60     | I/O |

|        | <b>T</b> ( | EMI A19*     | EMI 地址 19      | 7/0 |

|        | T6         | GPIO PIN61   | 第一组 GPIO61     | I/O |

|        |            | EMI A20*     | EMI 地址 20      |     |

|        | V6         | GPIO PIN62   | 第一组 GPIO62     | I/O |

|        |            | TIMER_IN2    | 定时器输入2         |     |

|        |            | EMI A21*     | EMI 地址 21      |     |

|        | U5         | GPIO PIN63   | 第一组 GPIO63     | I/O |

|        |            | TIMER IN3    | 定时器输入3         |     |

|        |            | EMI A22*     | EMI 地址 22      |     |

|        | U4         | 2ND GPIO32   | 第 2 组 GPIO32   | I/O |

|        |            | USB0 VBUSVLD | 未知             |     |

|        |            | EMI A23*     | EMI 地址 23      |     |

|        | V4 —       | SEN MCLK     | 未知             |     |

|        |            | EMI A24*     | EMI 地址 24      |     |

|        | V3         | I2S MCLK     | I2S 主时钟输出      | О   |

|        |            | EMI ADV      | 未知             |     |

| ARM    | Y4         | JTAG0 TCK    | A9 JTAG clk 信号 | I   |

| AINIVI | W5         | JTAG0 TMS    | A9 JTAG tms 信号 | I   |

| JTAG (5) | W4   | JTAG0_TDI      | A9 JTAG tdi 信号 | I   |  |

|----------|------|----------------|----------------|-----|--|

|          | V5   | JTAG0_TDO      | A9 JTAG tdo 信号 | О   |  |

|          | AA4  | JTAG0_TRSTN    | A9 JTAG 复位信号   | I   |  |

| OSC      | L1   | XTAL24M_IN     | 主晶振时钟输入        | I   |  |

| (2)      | M1   | XTAL24M_OUT    | 主晶振时钟输出        | О   |  |

|          | AE6  | ENET MII TXCLK | 以太网 MII 发送时钟   | I   |  |

|          | AE5  | ENET MDC       |                | О   |  |

| -        | AF4  | ENET_MDIO      |                | I/O |  |

|          | AF5  | ENET_RXCLK     | 以太网接收时钟        | I   |  |

|          | AG5  | ENET_TXCLK     | 以太网发送时钟        | О   |  |

|          | AG4  | ENET_CRS       | PHY CRS 信号     | I   |  |

| -        | AF6  | ENET_COL       | PHY 冲突信号,高有效   | I   |  |

| -        | AG6  | ENET_RXER      | PHY 接收错误,高有效   | I   |  |

|          | AG7  | ENET_RXDV      | PHY 接收数据有效,高有效 | I   |  |

| -        | AE7  | ENET_RXD0      | 以太网接收数据 0      | I   |  |

| -        | AF8  | ENET_RXD1      | 以太网接收数据 1      | I   |  |

| -        | AE8  | ENET_RXD2      | 以太网接收数据 2      | I   |  |

| ENET     | AH8  | ENET_RXD3      | 以太网接收数据 3      | I   |  |

| (27)     | AG9  | ENET_RXD4      | 以太网接收数据 4      | I   |  |

| (27)     | AG8  | ENET_RXD5      | 以太网接收数据 5      | I   |  |

|          | AE9  | ENET_RXD6      | 以太网接收数据 6      | I   |  |

|          | AF9  | ENET_RXD7      | 以太网接收数据 7      | I   |  |

|          | AG11 | ENET_TXER      | PHY 发送错误,高有效   | О   |  |

|          | AE10 | ENET_TXEN      | PHY 发送数据使能,高有效 | О   |  |

|          | AG10 | ENET_TXD0      | 以太网发送数据 0      | О   |  |

|          | AF11 | ENET_TXD1      | 以太网发送数据 1      | О   |  |

|          | AF12 | ENET_TXD2      | 以太网发送数据 2      | О   |  |

|          | AE12 | ENET_TXD3      | 以太网发送数据 3      | О   |  |

|          | AE11 | ENET_TXD4      | 以太网发送数据 4      | О   |  |

|          | AF13 | ENET_TXD5      | 以太网发送数据 5      | О   |  |

|          | AG13 | ENET_TXD6      | 以太网发送数据 6      | О   |  |

|          | AG12 | ENET_TXD7      | 以太网发送数据 7      | О   |  |

|          | B1   | XTAL32K_IN     | RTC 32K 时钟输入   | I   |  |

|          | C1   | XTAL32K_OUT    | RTC 32K 时钟输入   | О   |  |

| RTC (6)  | D1   | RTC_RESETN     | RTC 复位         | I   |  |

|          | E1   | RTC_BUTTON     |                |     |  |

|          | C2   | SOC_ISO_EN     |                |     |  |

|          | D2   | SOC_PMIC_EN    |                |     |  |

| SDIO     | A6   | SDIO_CCLK_OUT  | SDIO 时钟输出      | О   |  |

| (11)     | C7   | SDIO_CCMD      | SDIO 命令输出,高有效  | О   |  |

| (11)     | C5   | SDIO_CDATA0    | SDIO 数据 0      | I/O |  |

|                     | D5   | SDIO_CDATA1        | SDIO 数据 1                        | I/O |  |

|---------------------|------|--------------------|----------------------------------|-----|--|

|                     | F6   | SDIO_CDATA2        | SDIO 数据 2                        | I/O |  |

|                     | E6   | SDIO_CDATA3        | SDIO 数据 3                        | I/O |  |

|                     | D6   | SDIO_CDATA4        | SDIO 数据 4                        | I/O |  |

|                     | C6   | SDIO_CDATA5        | SDIO 数据 5                        | I/O |  |

|                     | D7   | SDIO_CDATA6        | SDIO 数据 6                        | I/O |  |

|                     | E7   | SDIO_CDATA7        | SDIO 数据 7                        | I/O |  |

|                     | В6   | SDIO_DATA_STROBE   | SDIO 数据选通信号                      | I   |  |

|                     | AK11 | MIPI_CK_N          | MIPI 差分时钟 N                      |     |  |

|                     | AJ11 | MIPI_CK_P          | MIPI 差分时钟 P                      |     |  |

|                     | AK9  | MIPI_D0_N          | MIPI 差分数据 0N                     |     |  |

| MIPI                | AJ9  | MIPI_D0_P          | MIPI 差分数据 0P                     |     |  |

|                     | AK10 | MIPI_D1_N          | MIPI 差分数据 1N                     |     |  |

| CSI2                | AJ10 | MIPI_D1_P          | MIPI 差分数据 1P                     |     |  |

| (11)                | AK12 | MIPI_D2_N          | MIPI 差分数据 2N                     |     |  |

|                     | AJ12 | MIPI D2 P          | MIPI 差分数据 2P                     |     |  |

|                     | AK13 | MIPI D3 N          | MIPI 差分数据 3N                     |     |  |

|                     | AJ13 | MIPI D3 P          | MIPI 差分数据 3P                     |     |  |

|                     | AH9  | MIPI REXT          |                                  |     |  |

|                     | AK19 | CMLINK RX X0 N     | Cameralink X 轴接收差分数据 0N          | I   |  |

|                     | AJ19 | CMLINK RX X0 P     | Cameralink X 轴接收差分数据 0P          | I   |  |

|                     | AK18 | CMLINK RX X1 N     | Cameralink X 轴接收差分数据 1N          | I   |  |

|                     | AJ18 | CMLINK RX X1 P     | Cameralink X 轴接收差分数据 1P          | I   |  |

|                     | AK16 | CMLINK RX XCLK N   | Cameralink X 轴接收差分时钟 N           | I   |  |

|                     | AJ16 | CMLINK RX XCLK P   | Cameralink X 轴接收差分时钟 P           | I   |  |

|                     | AK17 | CMLINK RX X2 N     | Cameralink X 轴接收差分数据 2N          | I   |  |

|                     | AJ17 | CMLINK RX X2 P     | Cameralink X 轴接收差分数据 2P          | I   |  |

|                     | AK15 | CMLINK_RX_X3_N     | Cameralink X 轴接收差分数据 3N          | I   |  |

| C                   | AJ15 | CMLINK_RX_X3_P     | Cameralink X 轴接收差分数据 3P          | I   |  |

| Camera<br>Link (43) | AF18 | CMLINK_SerTC_OUT_P | Cameralink 发送至数字相机的差<br>分串行通信 P  | О   |  |

|                     | AG18 | CMLINK_SerTC_OUT_N | Cameralink 发送至数字相机的差<br>分串行通信 N  | О   |  |

|                     | AG19 | CMLINK_SerTFG_INM  | 数字相机发送至 Cameralink 的差<br>分串行通信 M | I   |  |

|                     | AF19 | CMLINK_SerTFG_INP  | 数字相机发送至 Cameralink 的差<br>分串行通信 P | I   |  |

|                     | AE15 | CMLINK_RTUNE       |                                  |     |  |

|                     | AG17 | CMLINK_CC1_OUT_N   | Cameralink 差分控制信号 1N             | О   |  |

|                     | AF17 | CMLINK_CC1_OUT_P   | Cameralink 差分控制信号 1P             | О   |  |

|                     | AG16 | CMLINK CC2 OUT N   | Cameralink 差分控制信号 2N             | О   |  |

|       | AF16 | CMLINK_CC2_OUT_P | Cameralink 差分控制信号 2P    | О |  |

|-------|------|------------------|-------------------------|---|--|

|       | AG15 | CMLINK_CC3_OUT_N | Cameralink 差分控制信号 3N    | О |  |

|       | AF15 | CMLINK_CC3_OUT_P | Cameralink 差分控制信号 3P    | О |  |

|       | AG14 | CMLINK_CC4_OUT_N | Cameralink 差分控制信号 4N    | О |  |

|       | AF14 | CMLINK_CC4_OUT_P | Cameralink 差分控制信号 4P    | О |  |

|       | AG25 | CMLINK_RX_Y0_N   | Cameralink Y 轴接收差分数据 0N | I |  |

|       | AF25 | CMLINK_RX_Y0_P   | Cameralink Y 轴接收差分数据 0P | I |  |

|       | AG24 | CMLINK_RX_Y1_N   | Cameralink Y 轴接收差分数据 1N | I |  |

|       | AF24 | CMLINK_RX_Y1_P   | Cameralink Y 轴接收差分数据 1P | I |  |

|       | AG23 | CMLINK_RX_YCLK_N | Cameralink Y 轴接收差分时钟 N  | I |  |

|       | AF23 | CMLINK_RX_YCLK_P | Cameralink Y 轴接收差分时钟 P  | I |  |

|       | AG22 | CMLINK_RX_Y2_N   | Cameralink Y 轴接收差分数据 2N | I |  |

|       | AF22 | CMLINK_RX_Y2_P   | Cameralink Y 轴接收差分数据 2P | I |  |

|       | AG21 | CMLINK_RX_Y3_N   | Cameralink Y 轴接收差分数据 3N | I |  |

|       | AF21 | CMLINK_RX_Y3_P   | Cameralink Y 轴接收差分数据 3P | I |  |

|       | AK25 | CMLINK_RX_Z0_N   | Cameralink Z 轴接收差分数据 0N | I |  |

|       | AJ25 | CMLINK_RX_Z0_P   | Cameralink Z 轴接收差分数据 0P | I |  |

|       | AK24 | CMLINK_RX_Z1_N   | Cameralink Z 轴接收差分数据 1N | I |  |

|       | AJ24 | CMLINK_RX_Z1_P   | Cameralink Z 轴接收差分数据 1P | I |  |

|       | AJ23 | CMLINK_RX_ZCLK_N | Cameralink Z 轴接收差分时钟 N  | I |  |

|       | AK23 | CMLINK_RX_ZCLK_P | Cameralink Z 轴接收差分时钟 P  | I |  |

|       | AK22 | CMLINK_RX_Z2_N   | Cameralink Z 轴接收差分数据 2N | I |  |

|       | AJ22 | CMLINK_RX_Z2_P   | Cameralink Z 轴接收差分数据 2P | I |  |

|       | AK21 | CMLINK_RX_Z3_N   | Cameralink Z 轴接收差分数据 3N | I |  |

|       | AJ21 | CMLINK_RX_Z3_P   | Cameralink Z 轴接收差分数据 3P | I |  |

|       | C4   | USB0_ID          | USB0 OTG ID 检测信号        |   |  |

| USB-0 | A3   | USB0_VBUS        | USB0 电源线,接 5V 电源输入      | I |  |

| (5)   | B4   | USB0_DP          | USB0 差分数据信号正端           |   |  |

| (5)   | A4   | USB0_DM          | USB0 差分数据信号负端           |   |  |

|       | A5   | USB0_REXT        |                         |   |  |

| USB-1 | B2   | USB1_DP          | USB1 差分数据信号正端           |   |  |

| (3)   | A2   | USB1_DM          | USB1 差分数据信号负端           |   |  |

| (0)   | С3   | USB1_REXT        |                         |   |  |

|       | AJ5  | PCIE_REF_CLK_P   | PCIE 差分参考时钟输入 P         | I |  |

|       | AK5  | PCIE_REF_CLK_M   | PCIE 差分参考时钟输入 M         | I |  |

|       |      | PCIE_REXT        |                         |   |  |

| PCIe  | AE2  | PCIE_TX0_P       | PCIE 差分数据发送 0P          | О |  |

| (19)  | AE1  | PCIE_TX0_M       | PCIE 差分数据发送 0M          | О |  |

|       | AJ3  | PCIE_RX0_P       | PCIE 差分数据接收 0P          | I |  |

|       | AK3  | PCIE_RX0_M       | PCIE 差分数据接收 0M          | I |  |

|       | AF2  | PCIE_TX1_P       | PCIE 差分数据发送 1P          | О |  |

|              | AF1 | PCIE_TX1_M      | PCIE 差分数据发送 1M     | О |  |

|--------------|-----|-----------------|--------------------|---|--|

|              | AJ4 | PCIE_RX1_P      | PCIE 差分数据接收 1P     | I |  |

|              | AK4 | PCIE_RX1_M      | PCIE 差分数据接收 2M     | I |  |

|              | AG2 | PCIE_TX2_P      | PCIE 差分数据发送 2P     | О |  |

|              | AG1 | PCIE_TX2_M      | PCIE 差分数据发送 2M     | О |  |

|              | AJ6 | PCIE_RX2_P      | PCIE 差分数据接收 2P     | I |  |

|              | AK6 | PCIE_RX2_M      | PCIE 差分数据接收 2M     | I |  |

|              | AH2 | PCIE_TX3_P      | PCIE 差分数据发送 3P     | О |  |

|              | AH1 | PCIE_TX3_M      | PCIE 差分数据发送 3M     | О |  |

|              | AJ7 | PCIE_RX3_P      | PCIE 差分数据接收 3P     | I |  |

|              | AK7 | PCIE_RX3_M      | PCIE 差分数据接收 3M     | I |  |

|              | P2  | SRIO_RX0_P      | RapidIO 差分数据接收 0P  | I |  |

|              | P1  | SRIO_RX0_M      | RapidIO 差分数据接收 0M  | I |  |

|              | W2  | SRIO_TX0_P      | RapidIO 差分数据发送 0P  | O |  |

|              | W1  | SRIO_TX0_M      | RapidIO 差分数据发送 0M  | О |  |

|              | R2  | SRIO_RX1_P      | RapidIO 差分数据接收 1P  | I |  |

|              | R1  | SRIO_RX1_M      | RapidIO 差分数据接收 1M  | I |  |

|              | Y2  | SRIO_TX1_P      | RapidIO 差分数据发送 1P  | О |  |

|              | Y1  | SRIO_TX1_M      | RapidIO 差分数据发送 1M  | О |  |

| RapidIO      | T2  | SRIO_RX2_P      | RapidIO 差分数据接收 2P  | I |  |

| (20)         | T1  | SRIO_RX2_M      | RapidIO 差分数据接收 2M  | I |  |

| (20)         | AB2 | SRIO_TX2_P      | RapidIO 差分数据发送 2P  | О |  |

|              | AB1 | SRIO_TX2_M      | RapidIO 差分数据发送 2M  | О |  |

|              | U2  | SRIO_RX3_P      | RapidIO 差分数据接收 3P  | I |  |

|              | U1  | SRIO_RX3_M      | RapidIO 差分数据接收 3M  | I |  |

|              | AC2 | SRIO_TX3_P      | RapidIO 差分数据发送 3P  | О |  |

|              | AC1 | SRIO_TX3_M      | RapidIO 差分数据发送 3M  | О |  |

|              | AA2 | SRIO_REF_CLK_P  | RapidIO 差分参考时钟输入 P | I |  |

|              | AA1 | SRIO_REF_CLK_M  | RapidIO 差分参考时钟输入 M | I |  |

|              | AA3 | SRIO_RESREF     |                    |   |  |

|              | J11 | LDO_VIP8O       |                    |   |  |

|              | A26 | LVDS_TX_TA0N    | LVDS 差分数据通道 0N     | О |  |

|              | B26 | LVDS_TX_TA0P    | LVDS 差分数据通道 0P     | О |  |

| Display (20) | A25 | LVDS_TX_TA1N    | LVDS 差分数据通道 1N     | О |  |

|              | B25 | LVDS_TX_TA1P    | LVDS 差分数据通道 1P     | О |  |

|              | A23 | LVDS_TX_TA2N    | LVDS 差分数据通道 2N     | О |  |

|              | B23 | LVDS_TX_TA2P    | LVDS 差分数据通道 2P     | О |  |

|              | A22 | LVDS_TX_TA3N    | LVDS 差分数据通道 3N     | О |  |

|              | B22 | LVDS_TX_TA3P    | LVDS 差分数据通道 3P     | О |  |

|              | A24 | LVDS_TX_TAACLKN | LVDS 差分时钟通道 AAN    | О |  |

|              | B24 | LVDS TX TAACLKP | LVDS 差分时钟通道 AAP    | О |  |

|       | A19 | LVDS_TX_TABCLKN  | LVDS 差分时钟通道 ABN | О   |

|-------|-----|------------------|-----------------|-----|

|       | B19 | LVDS_TX_TABCLKP  | LVDS 差分时钟通道 ABP | 0   |

|       | A21 | LVDS_TX_TA4N     | LVDS 差分数据通道 4N  | 0   |

|       | B21 | LVDS_TX_TA4P     | LVDS 差分数据通道 4P  | 0   |

|       | A20 | LVDS_TX_TA5N     | LVDS 差分数据通道 5N  | 0   |

|       | B20 | LVDS_TX_TA5P     | LVDS 差分数据通道 5P  | 0   |

|       | A18 | LVDS_TX_TA6N     | LVDS 差分数据通道 6N  | 0   |

|       | B18 | LVDS_TX_TA6P     | LVDS 差分数据通道 6P  | 0   |

|       | A17 | LVDS_TX_TA7N     | LVDS 差分数据通道 7N  | 0   |

|       | B17 | LVDS_TX_TA7P     | LVDS 差分数据通道 7P  | 0   |

|       | C22 | LVDS_TX_RTUNE    |                 |     |

|       | A28 | PAD_MEM_DATA[0]  | DDR 数据信号 0      | I/O |

|       | A29 | PAD_MEM_DATA[1]  | DDR 数据信号 1      | I/O |

|       | G26 | PAD_MEM_DATA[10] | DDR 数据信号 10     | I/O |

|       | E27 | PAD_MEM_DATA[11] | DDR 数据信号 11     | I/O |

|       | G28 | PAD_MEM_DATA[12] | DDR 数据信号 12     | I/O |

|       | D27 | PAD_MEM_DATA[13] | DDR 数据信号 13     | I/O |

|       | D28 | PAD_MEM_DATA[14] | DDR 数据信号 14     | I/O |

|       | G27 | PAD_MEM_DATA[15] | DDR 数据信号 15     | I/O |

|       | H25 | PAD_MEM_DATA[16] | DDR 数据信号 16     | I/O |

|       | H27 | PAD_MEM_DATA[17] | DDR 数据信号 17     | I/O |

|       | H28 | PAD_MEM_DATA[18] | DDR 数据信号 18     | I/O |

|       | J25 | PAD_MEM_DATA[19] | DDR 数据信号 19     | I/O |

|       | B28 | PAD_MEM_DATA[2]  | DDR 数据信号 2      | I/O |

| DDR   | K25 | PAD_MEM_DATA[20] | DDR 数据信号 20     | I/O |

| אטט   | K26 | PAD_MEM_DATA[21] | DDR 数据信号 21     | I/O |

| (172) | K28 | PAD_MEM_DATA[22] | DDR 数据信号 22     | I/O |

|       | K27 | PAD_MEM_DATA[23] | DDR 数据信号 23     | I/O |

|       | F29 | PAD_MEM_DATA[24] | DDR 数据信号 24     | I/O |

|       | G29 | PAD_MEM_DATA[25] | DDR 数据信号 25     | I/O |

|       | G30 | PAD_MEM_DATA[26] | DDR 数据信号 26     | I/O |

|       | J29 | PAD_MEM_DATA[27] | DDR 数据信号 27     | I/O |

|       | K30 | PAD_MEM_DATA[28] | DDR 数据信号 28     | I/O |

|       | K29 | PAD_MEM_DATA[29] | DDR 数据信号 29     | I/O |

|       | C29 | PAD_MEM_DATA[3]  | DDR 数据信号 3      | I/O |

|       | M30 | PAD_MEM_DATA[30] | DDR 数据信号 30     | I/O |

|       | M29 | PAD_MEM_DATA[31] | DDR 数据信号 31     | I/O |

|       | W29 | PAD_MEM_DATA[32] | DDR 数据信号 32     | I/O |

|       | V30 | PAD_MEM_DATA[33] | DDR 数据信号 33     | I/O |

|       | U30 | PAD_MEM_DATA[34] | DDR 数据信号 34     | I/O |

|       | V29 | PAD_MEM_DATA[35] | DDR 数据信号 35     | I/O |

| T29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                  |                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|-----------------------------------------|-----|